# Designing Chiplet-Based 2.5D High-Interconnect Density Semiconductor Packages:

**Challenges and Considerations**

HANA Micron CTO D.H. Jayden Kim

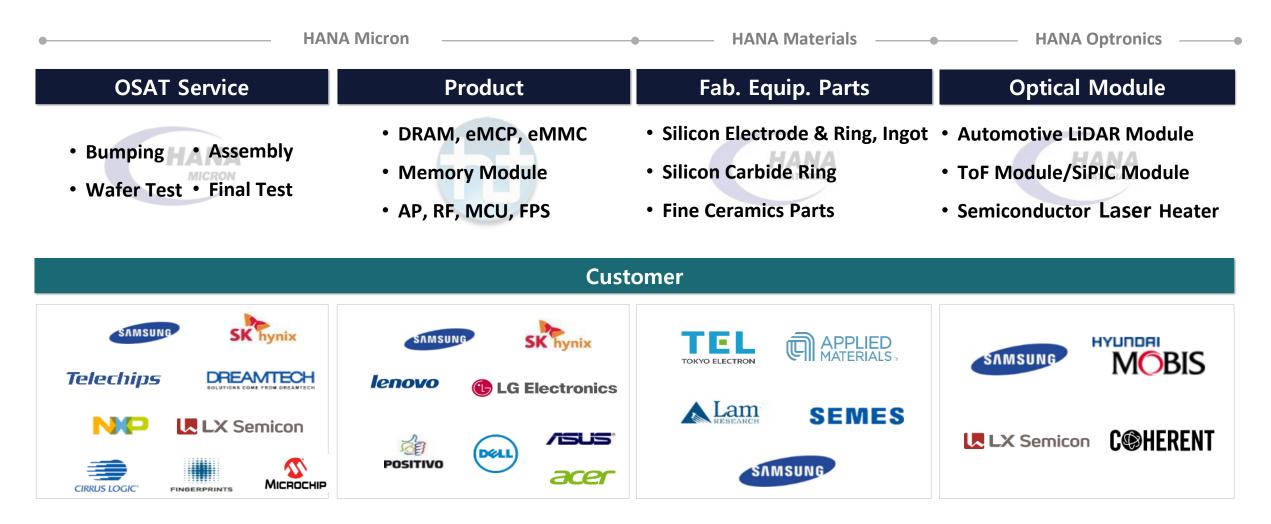

### HANA Micron Corporate Overview

"HANA Micron is a leading Semiconductor Package Turnkey Solution Provider in Korea"

- 2 -

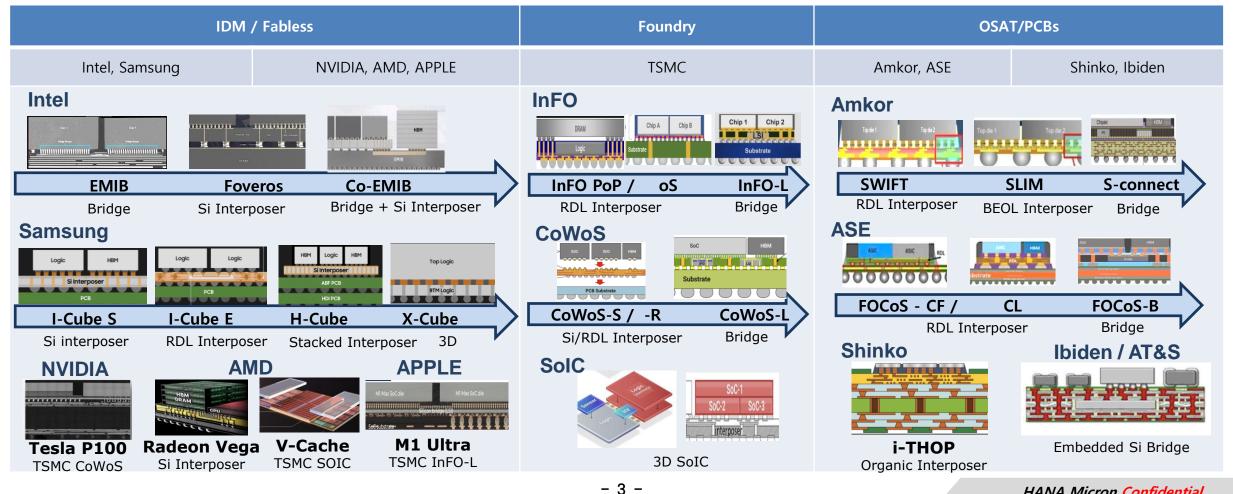

### Chiplet Based Advanced Packaging Technology Overview

- Foundries and IDMs : Developing in-house and Establishing a Tech. Platform including 3D and 2.5D  $\rightarrow$  preventing true heterogeneous integration of chiplets from different foundries.

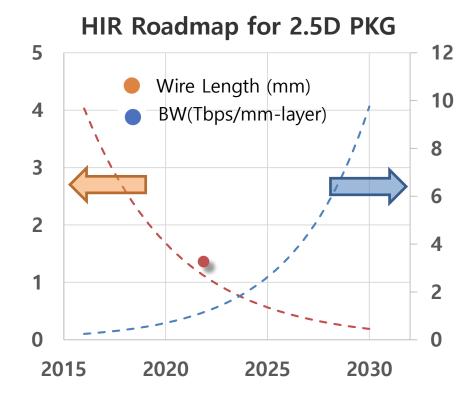

- **OSATs**: Focusing on Backend 2.5D Integration. Silicon Interposer, RDL Interposer and Silicon Bridge

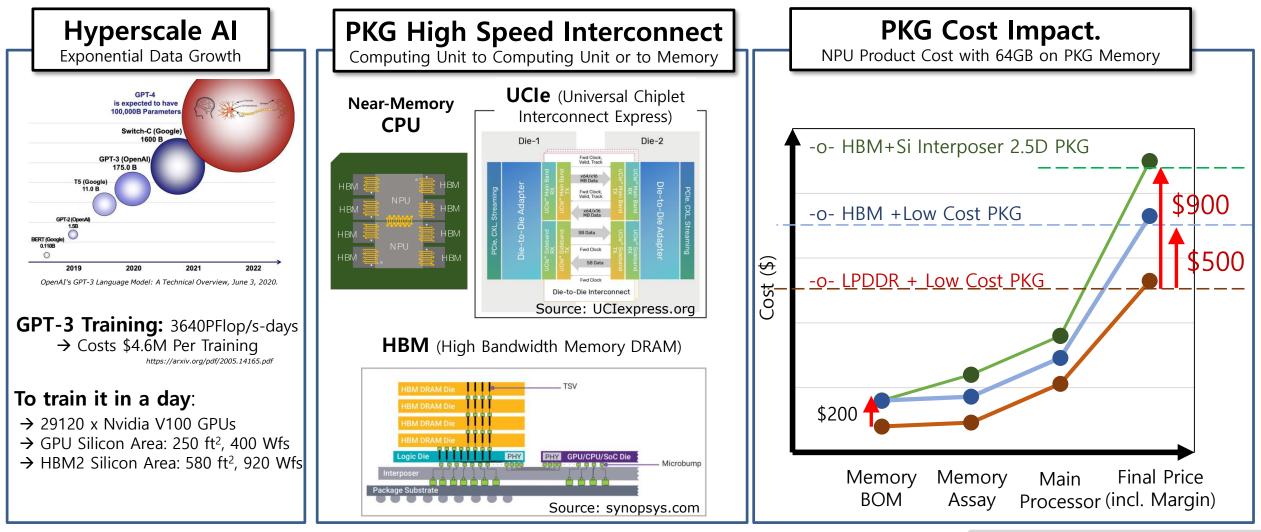

### Demand for Interconnect Standard & Low Cost 2.5D Tech. Solution

#### • Al Computing Power : outpaces Moore's law.

$\rightarrow$ In-PKG Interconnect standard for lower design cost and OSAT need to develop low cost PKG technology.

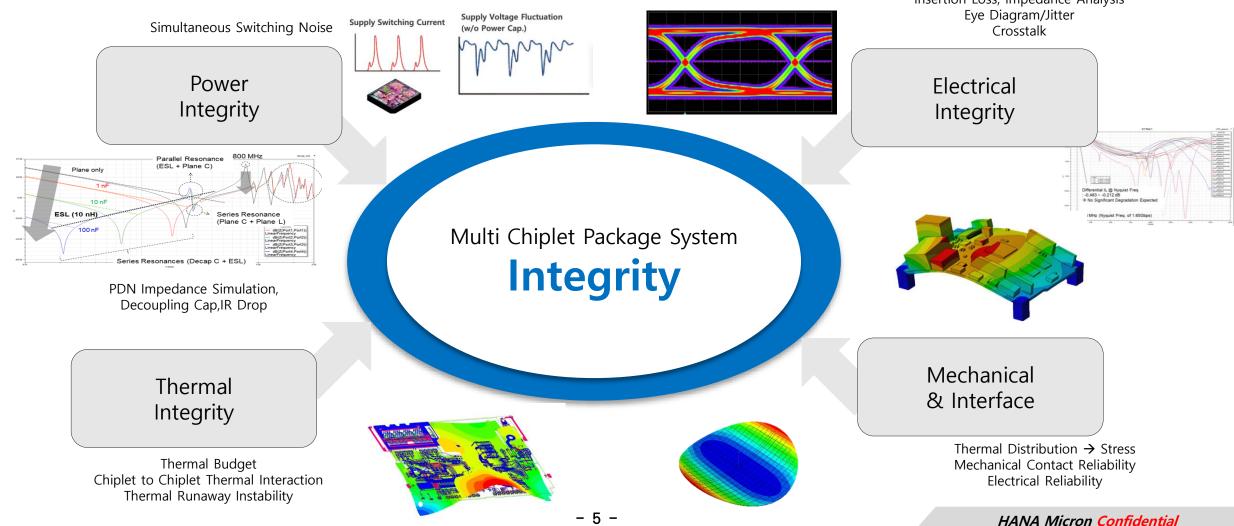

# Package Design Verification

### □ Interaction Verification

User-friendly design flows require the creation of signal, power, thermal and mechanical models for the IC, package and PCB which are then combined for system-level simulation.

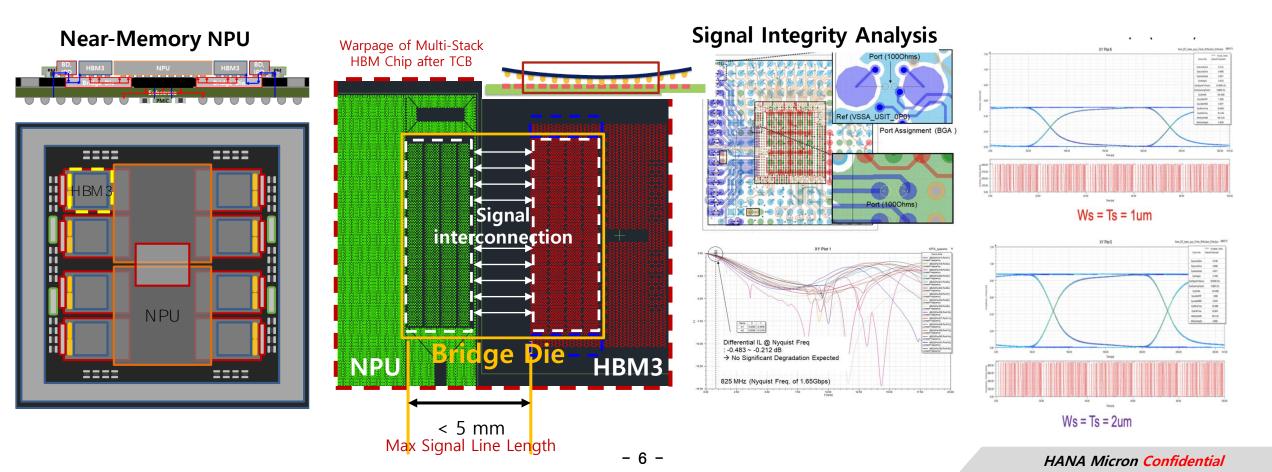

# Near Memory NPU – HBM3 Signal Line Design

□ HBM3 chip dimension: > 3000 I/Os per 8mm Signal Width & max 5mm Signal Line

□ **SI Anlaysis:** due to large insertion loss (Long Signal Line), L/S >2um Signal Line needed.

$\rightarrow$  Limiting Linear Escape Density to 250 I/O per mm-Layer, SERDES needed for future Gen.

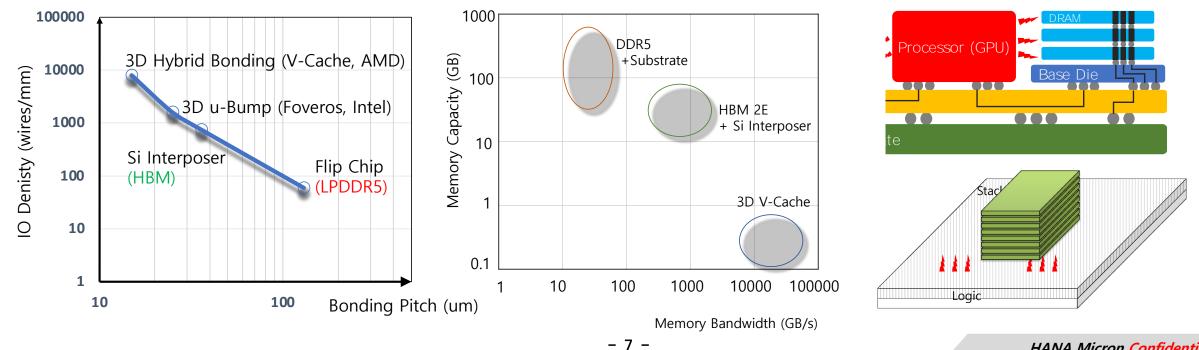

## 3D Stacked Memory drastically boost Bandwidth

**3D Stacked Memory on Processor:** Highest Memory Bandwidth Possible.

$\rightarrow$  AMD's V Cache SRAM: <32MB. Too small for large parameter deep learning.

HBM on Processor or Processor in HBM: DRAM's operating temperature is limited < 85C°

$\rightarrow$  Processing unit's performance is limited by thermal budget.

High Operating Temperature + High Speed + High Density Memory + High Endurance Needed

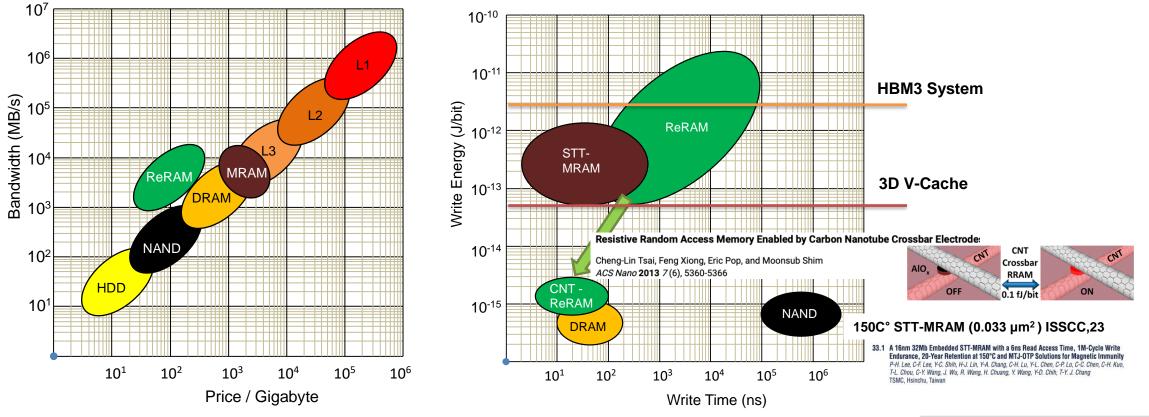

## 3D Stackable Memory Candidates

□ MRAM and ReRAM have potentials: Similar cost and read bandwidth to DRAM.

- $\rightarrow$  Nano-technology (ex. CNT) might help reducing the Write Energy.

- $\rightarrow$  By sacrificing retention, operating temperature might be increased.

□ Further New Memory Device Research needed for more efficient AI Processor.

# Optical Interconnects between Chip Packages

CPO (Co-Packaged Optics): Silicon Photonics in Chiplet PKG.

→ Waveguide, Modulator, PD, WDM Filter, DeMux, Coupler etc.

**BW Target: >1Tbps/mm @ distance up to a few km** (w/2.5D requires <5mm short distance)

# Conclusion

□ OSATs are developing low cost 2.5D Advanced Packaging Technology.

- Power, Electrical, Thermal and Stress integrities must be thoroughly examined.

- □ 3D Stacking of Memory to drastically improve the Memory Bandwidth

- □ Novel Memory operating at higher temperature is needed

- □ Optical Interconnect started to be co-integrated in same package.

- □ Collaboration with USA research group played a vital role.

- $\rightarrow$  Past a few years, worked with USA Universities on optoelectronics projects funded by Korean Government.

- → Collaboration ended due to classification of the project as a National Security Tech.

- $\rightarrow$  Advanced Packaging Technology is currently classified as a National Core Tech.

□ In Semiconductor Advanced Packaging Field, NSF and Korea Government Joint Research Program would facilitate further collaboration between two countries.